# Test Method to Evaluate High-g Component Susceptibility

**2018 NDIA Fuze Conference** San Diego, CA

Daniel Peairs, Nathan Millard, Triet Dao, Marc Worthington L3 Defense Electronic Systems

Ericka Amborn, Frank Marso, Craig Doolittle Applied Research Associates, Inc.

May 2018

DISTRIBUTION A. Approved for public release: distribution unlimited PUBLIC RELEASE. Cleared by United States Army Armament Research, Development and Engineering Center (ARDEC) for public release under PAO Log No. 401-18 and 402-18 on April 24, 2018.

# L3 Defense Electronic Systems (L3 DES)

Over 75 years of solving our customers' hardest problems

# Introduction

- Fuze level testing under severe loading conditions:

- Expensive

- May not identify risk early in design process

- Difficult to pinpoint cause of fuze level failures

- Components may function normally post-test despite intra-test failure

The test methodology discussed here allows for a single electronic component to be tested and actively monitored during a shock event.

# **ESAD Electronics Characterization and Survivability**

- Single Hopkinson Bar Testing

- Conduct high acceleration/high frequency testing of select electronic components

- Modeling of components and FEA

- Correlate high fidelity FEA models of components with empirical results

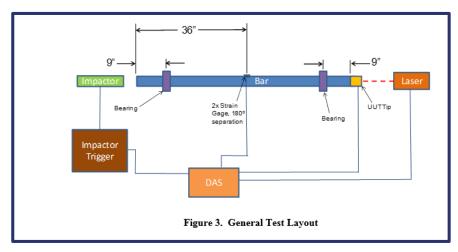

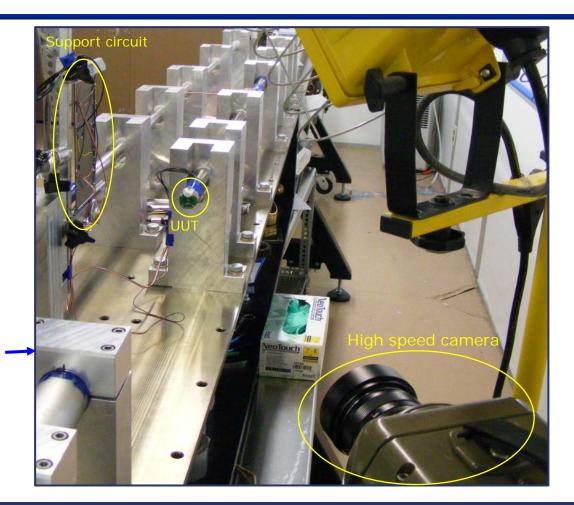

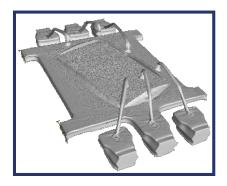

## Test Set Up

- Single Hopkinson Bar

- Steel Striker

- Steel Bar

- Threaded interface for tip

- PCB mounted to tip with single component

- Strain gauges

- Laser vibrometer

#### **Test Overview**

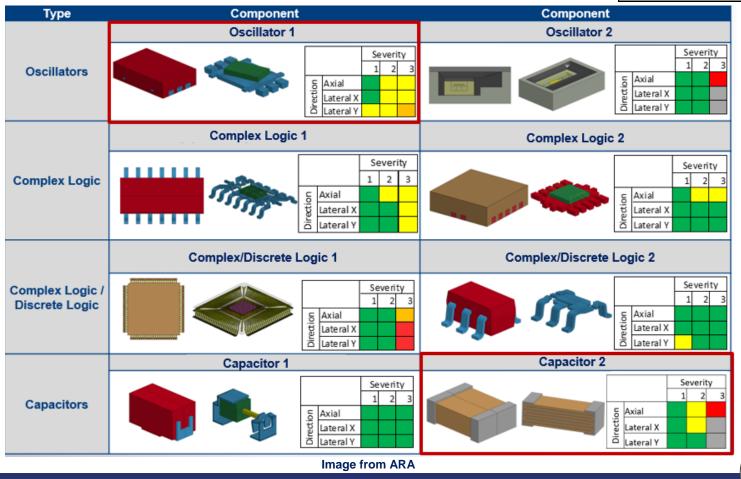

- Single Hopkinson Bar testing included 3 each of 8 different components commonly used in L3 DES designs

- Tested at 3 different acceleration severity levels

- System capable of producing pulses ranging from 1000 g's to over 250,000 g's

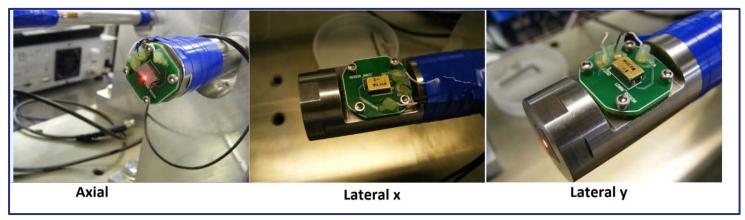

- Each component tested in an axial and 2 lateral configurations

## **Downselected Component List**

• Selected based on size, availability or previous history in survivable firesets

| Component Type | Description                                         |  |  |

|----------------|-----------------------------------------------------|--|--|

| Oscillator     | Oscillator 1 - Delay block                          |  |  |

| Oscillator     | Oscillator 2 - Oscillator for logic timing          |  |  |

| Complex Logic  | Complex Logic 1 - Leaded microcontroller            |  |  |

| Complex Logic  | Complex Logic 2 - Bottom terminated microcontroller |  |  |

| Complex Logic  | Complex Logic 3 - FPGA                              |  |  |

| Discrete Logic | Schmitt Trigger                                     |  |  |

| Capacitor      | Capacitor 1 - Tantalum capacitor                    |  |  |

| Capacitor      | Capacitor 2 - Ceramic capacitor                     |  |  |

## **Test Methodology**

- A set of inputs was selected for each individual component in this test. The expected behavior of each component was characterized and recorded before, during, and after each test. Any change in the output was evaluated and analyzed using the appropriate failure analysis method.

- The output data was correlated against the strain gage derived acceleration

| Component          | Input                                            | Expected Output                                                                                                 |  |

|--------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|

| Oscillator 2       | 5V, GND                                          | 8MHz Output                                                                                                     |  |

| Schmitt Trigger    | 5V, GND<br>100kHz, 50% duty cycle, 0-5V          | Inversion of the input                                                                                          |  |

| Oscillator 1       | 3.3V, GND<br>50 kHz, 75% duty cycle, 0-3.3V      | Output rises 10us after input is enabled. Falls when input is falling.                                          |  |

| Complex Logic 1    | 3.3V, GND                                        | Nominal: 50kHz, 50% duty cycle<br>Reset: 75kHz, 50% duty cycle for ~100us before<br>resuming normal operation   |  |

| Complex Logic 2    | 3.3V, GND                                        | Nominal: 100kHz, 50% duty cycle<br>Reset: 200kHz, 50% duty cycle for ~100us before<br>resuming normal operation |  |

| Complex Logic 3    | 3.3V, 2.5V, GND<br>Negative reset,<br>8MHz clock | Nominal: 125kHz, 50% duty cycle<br>Reset: 500kHz, 50% duty cycle for ~100us before<br>resuming normal operation |  |

| Tantalum Capacitor | 19kHz, 20% duty cycle, 0-5V                      | RC charging triangular waveform from 0V to around 3.2V depending on capacitance                                 |  |

| Ceramic Capacitor  | 800Hz, 20% duty cycle, 0-5V                      | RC charging triangular waveform from 0V to around 3.2V depending on capacitance                                 |  |

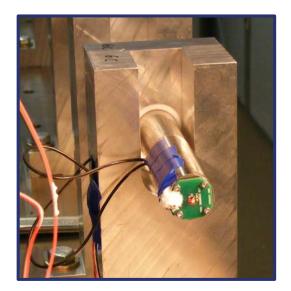

# **Test Setup**

Laser vibrometer protection

PUBLIC RELEASE. Use or disclosure of data contained on this sheet is subject to the restrictions on the title page of this document.

# **Results Summary**

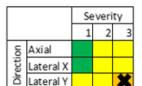

Key

Measured Test Severity

Unaffected

Affected During Test

Affected Post Test

Part Failed

Test Not Conducted Due to Previous Failure

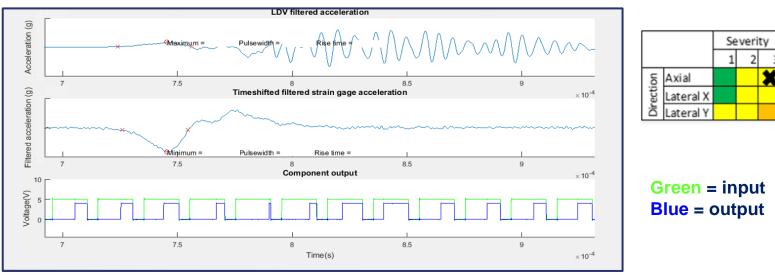

# **Oscillator 1 – Axial Impact at Severity Level 3**

**Round 3 Axial Configuration**

- Delays both greater and smaller than the expected 10us can be observed in the above figure.

- In the current setup for a 10us delay, a delay shift as great as ~70% can be observed in an individual pulse. It's unlikely this delay shift would scale in a 10ms set up.

- Further testing is required to verify this claim.

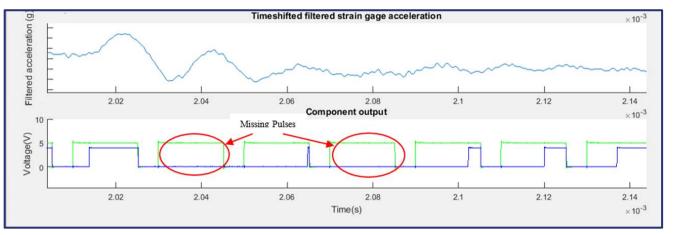

#### **Oscillator 1 – Lateral Y at Severity Level 3**

**Round 3 Lateral Y Configuration**

- Missing pulses indicate component malfunction

- Component showed a small, permanent increase in on-time pulse width after the test

**Green** = input **Blue** = output

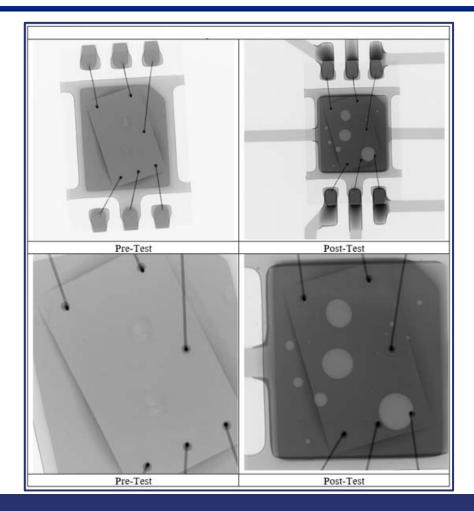

# **Oscillator 1 – Post Test Imaging**

- Pre and post-test high resolution x-rays were conducted on all components

- Internal bond wires appear to be intact

• CT Scans also conducted to better understand internal geometries

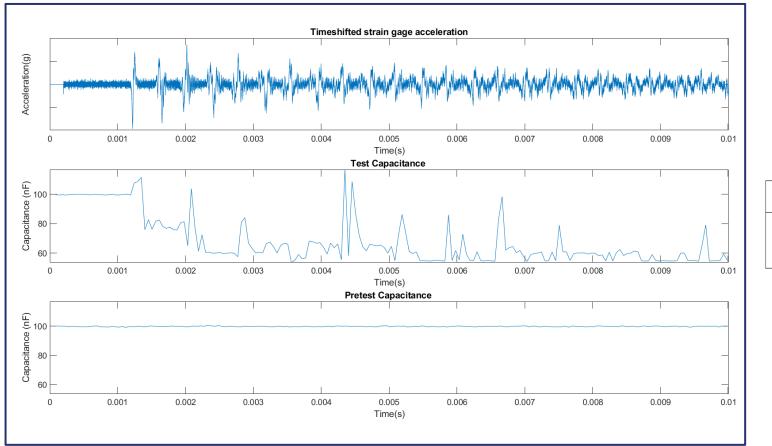

#### **Ceramic Capacitor – Axial at Severity Level 3**

#### **Ceramic Capacitor – Axial at Severity Level 3**

|           | Computed Capacitance (nF) |        |        |                       |  |

|-----------|---------------------------|--------|--------|-----------------------|--|

|           | Min                       | Max    | Mean   | Standard<br>Deviation |  |

| Pre-Test  | 105.57                    | 106.86 | 106.32 | 0.232                 |  |

| Test      | 55.70                     | 117.63 | 71.34  | 17.56                 |  |

| Post-Test | 61.37                     | 62.15  | 61.69  | 0.145                 |  |

- 42% decrease in capacitance was observed

- High resolution x-rays were not able to identify damage within capacitor layers

## **Component Testing Summary**

- Developed enhanced methodology for assessing component susceptibility to high shock environments

- Evaluated several classes of components commonly used in ESADs

- Actively monitored single components during a shock event

- Permits assessment of risk during High-g events that is not possible with pre and post test interrogation only

#### Acknowledgements

- This work was funded by the DoD Ordnance Technology Consortium (DOTC) agreement W15QKN-09-1001, W15QKN-09-12-001, 15-01-INIT299

- The authors are grateful for the support of and Justin Bruno of ARA and Perry Salyers of L3 DES.