# Process Performance Models for Hardware Engineers

# **CMMI Technology Conference**

November 15-18

**Tom Fosness**

Mechanical Systems Engineering Process Improvement Lead Northrop Grumman Corp., Electronic Systems Sector

**Rolling Meadows**

# First a Brief Story...

Work Product Inspection Error Density Analysis

High Maturity???

*Error Prediction and Removal Process-Performance Model*

> Equivalent Effort Source Lines of Code

2

# **Drawing Normalization**

- Kind of drawing

- Number of Sheets

- Lines of Notes

- Drawing Originator

- Drawing Complexity

| Κ | S | L | 0 | С |

|---|---|---|---|---|

| i | h | i | r | 0 |

| n | е | n | i | m |

| d | е | е | g | р |

|   | t | S | i | I |

|   | S |   | n | е |

|   |   | 0 | а | Х |

|   |   | f | t | i |

|   |   |   | 0 | t |

|   |   | n | r | у |

|   |   | 0 |   |   |

|   |   | t |   |   |

|   |   | е |   |   |

|   |   | S |   |   |

- Goals

- Give hardware engineers an idea of where to start when devising PPMs

- Provide some guidance on developing PPMs

- Teach tactics and techniques that hardware engineers can put directly to use

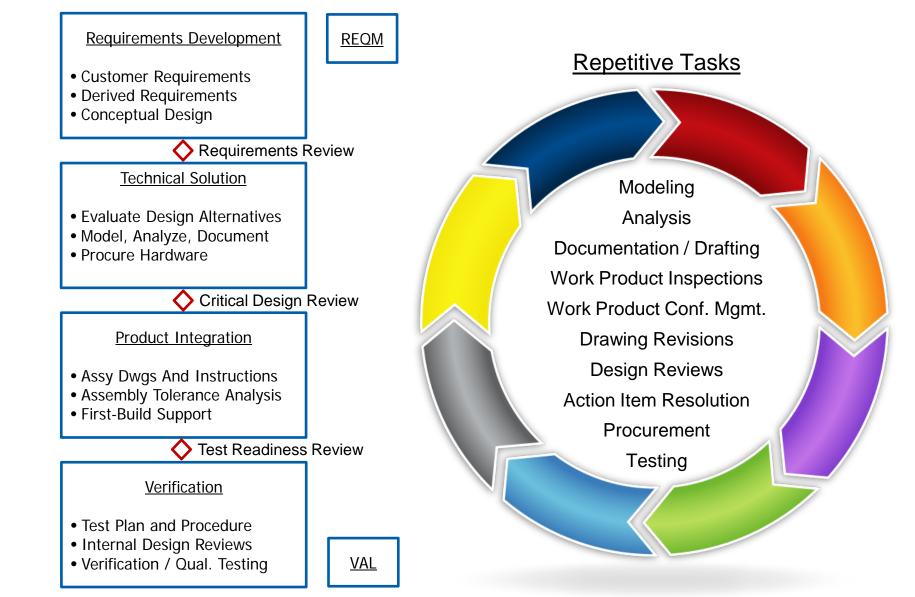

- Agenda

- General guidance on PPMs

- Look at common hardware development processes and identify some aspects that lend themselves to modeling

- Identify what we want to predict and what measures and baselines are needed to establish a model

- Look at some modeling techniques and some examples of hardware PPMs used at Northrop Grumman Electronic Systems, Rolling Meadows

- Talk about the value and potential benefits of these models

NORTHROP GRUMMAN

NORTHROP GRUMMAN

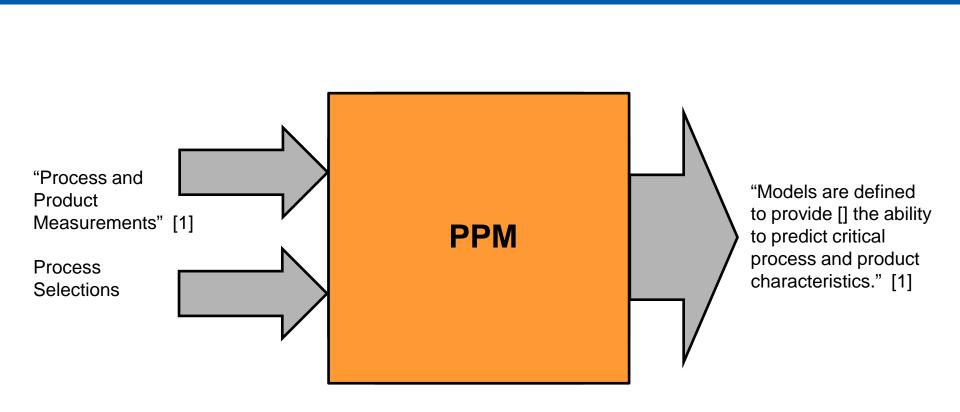

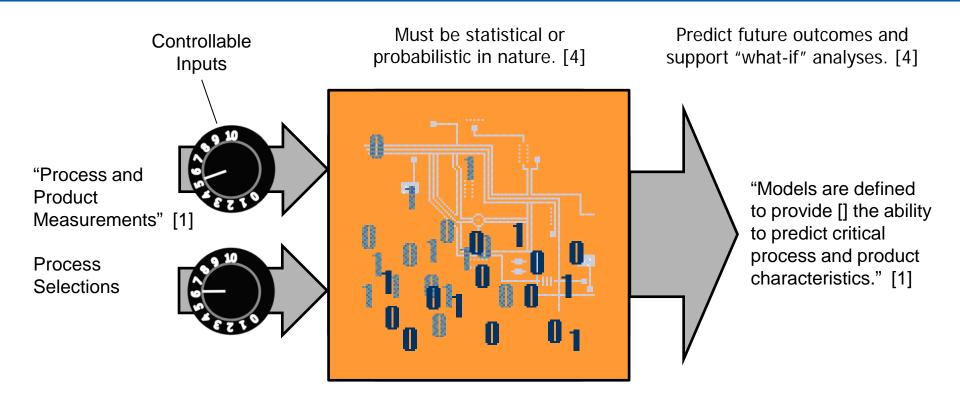

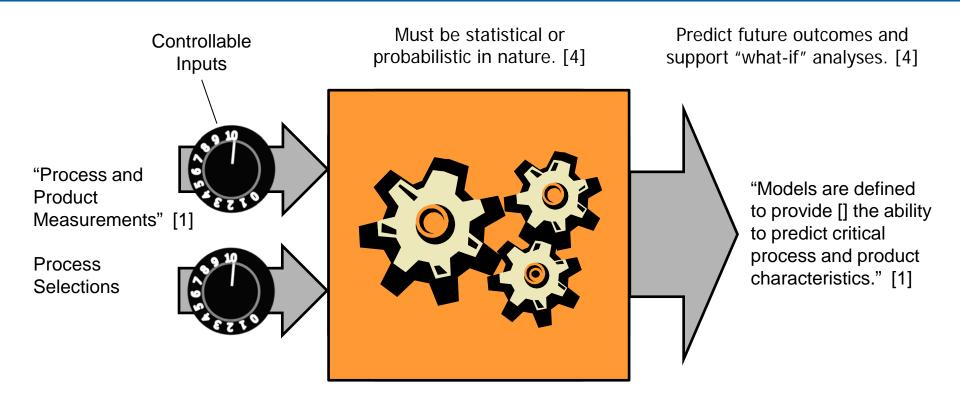

PPM Uses:

- Predict Process or Product Characteristics

- Evaluate the impact of process composition

- Evaluate the impact of processes measurements on performance relative to objectives

# **Process Performance Model Development**

## What do Hardware Engineers Do?

11

## What do Hardware Engineers Do? (Translation)

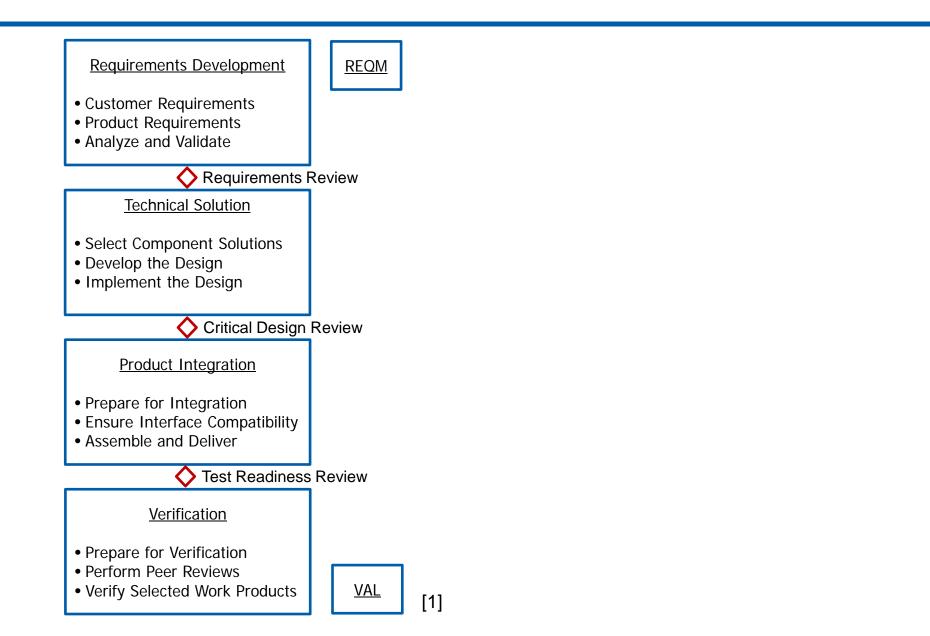

# Identifying Processes and Measures that Impact Key Characteristics

|                             | Quality Characteristics |                  |                      |                        |                          |                | Process-Performance Characteristics |                   |                    |                |  |  |  |  |

|-----------------------------|-------------------------|------------------|----------------------|------------------------|--------------------------|----------------|-------------------------------------|-------------------|--------------------|----------------|--|--|--|--|

| Process Area                | Size &<br>Weight        | Product<br>Perf. | Product<br>Endurance | Product<br>Reliability | Customer<br>Satisfaction | Manuf.<br>Cost | Assembly<br>Cost                    | Lifecycle<br>Cost | Escaped<br>Defects | Cycle<br>Times |  |  |  |  |

| Requirements<br>Development |                         |                  |                      |                        |                          |                |                                     |                   |                    |                |  |  |  |  |

| Technical<br>Solutions      |                         |                  |                      |                        |                          |                |                                     |                   |                    |                |  |  |  |  |

| Product<br>Integration      |                         |                  |                      |                        |                          |                |                                     |                   |                    |                |  |  |  |  |

| Verification                |                         |                  |                      |                        |                          |                |                                     |                   |                    |                |  |  |  |  |

| Modeling                    |                         |                  |                      |                        |                          |                |                                     |                   |                    |                |  |  |  |  |

| Analysis                    |                         |                  |                      |                        |                          |                |                                     |                   |                    |                |  |  |  |  |

| Doc / Drafting              |                         |                  |                      |                        |                          |                |                                     |                   |                    |                |  |  |  |  |

| WPI                         |                         |                  |                      |                        |                          |                |                                     |                   |                    |                |  |  |  |  |

| СМ                          |                         |                  |                      |                        |                          |                |                                     |                   |                    |                |  |  |  |  |

| Drawing Revs                |                         |                  |                      |                        |                          |                |                                     |                   |                    |                |  |  |  |  |

| Reviews                     |                         |                  |                      |                        |                          |                |                                     |                   |                    |                |  |  |  |  |

| AI Resolution               |                         |                  |                      |                        |                          |                |                                     |                   |                    |                |  |  |  |  |

| Procurement                 |                         |                  |                      |                        |                          |                |                                     |                   |                    |                |  |  |  |  |

| Testing                     |                         |                  |                      |                        |                          |                |                                     |                   |                    |                |  |  |  |  |

| Product                     |                         |                  |                      |                        |                          |                |                                     |                   |                    |                |  |  |  |  |

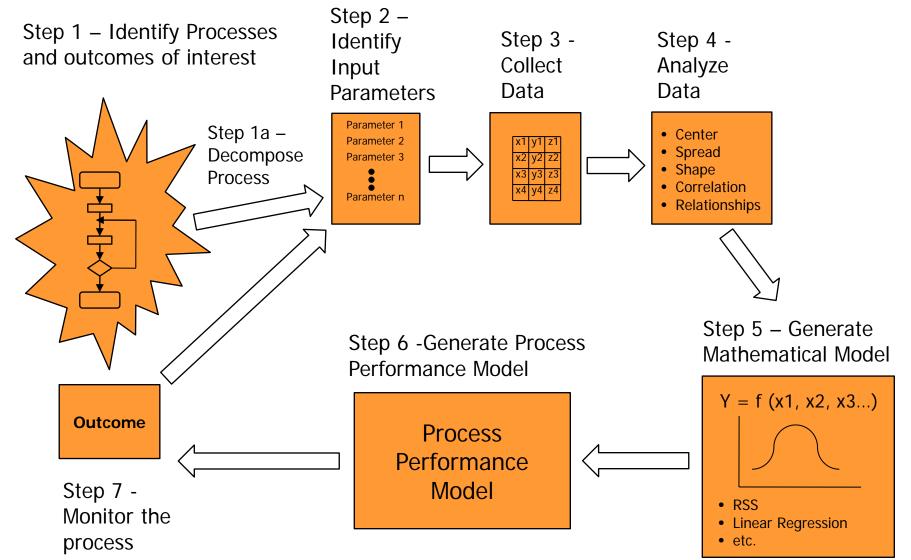

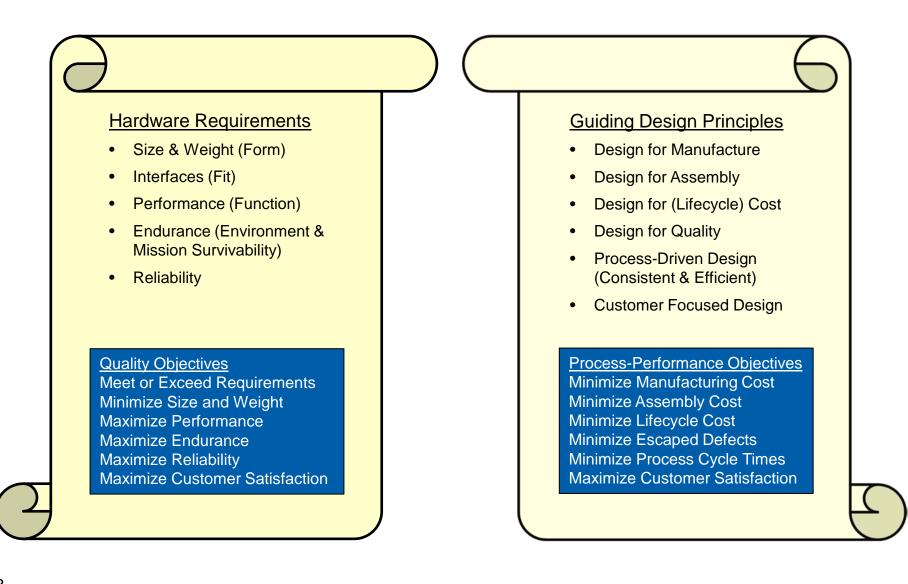

- Requirements Development

- How will the vibration requirement affect the product development time and cost?

- How does the quantity of requirements affect the development time and cost?

- How does requirements maturity affect task on-time completions?

- Technical Solutions

- How does analysis conservatism impact cost, schedule, quality? Test success?

- How does design time impact integration, test, manufacture, and assembly time?

- How do process selections to create prototypes and perform preliminary testing affect development cost?

- Product Integration

- How does standard part usage, design reuse, and other part selections affect procurement time?

- How does the tolerance stack method affect assembly quality?

- How does component testing affect assembly time?

- Verification

- How does the level of testing affect product reliability?

- How does verification method (similarity, analysis, test) affect development cost?

- Product

- How does product complexity affect schedule, cost, and quality?

- How do Technical Performance Measures predict success/risk for the program?

- How does design decisions influence the manufacturing process?

- How does part count affect assembly time?

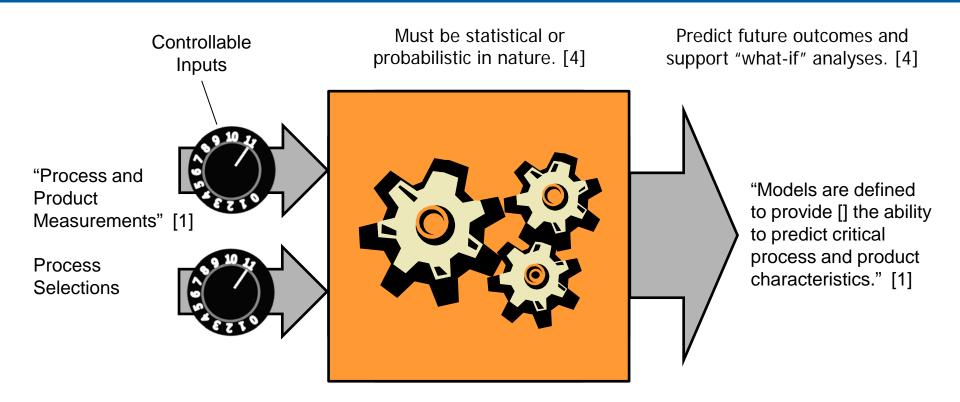

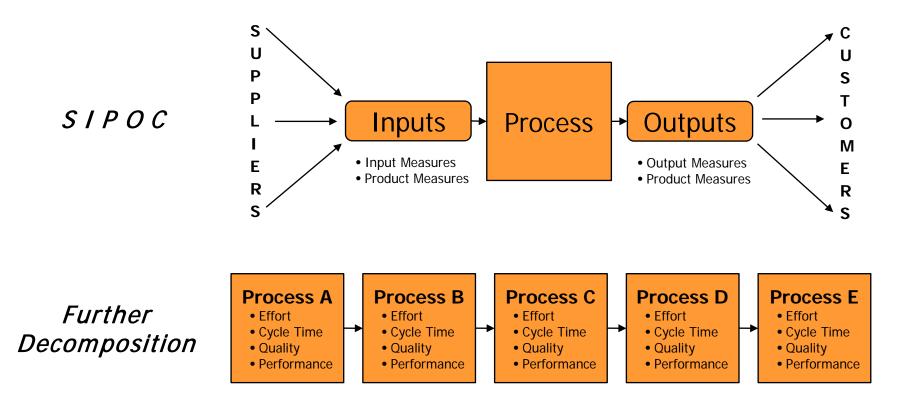

Decomposing the Process and Identifying Input Parameters

- · Decompose until sub-process is measureable

- For each sub-process try to identify each of the following measures:

- Effort Measure (labor hours)

- Cycle Time Measure (schedule)

- Quality Measure (errors / defects)

- Performance Measure (yield / efficiency)

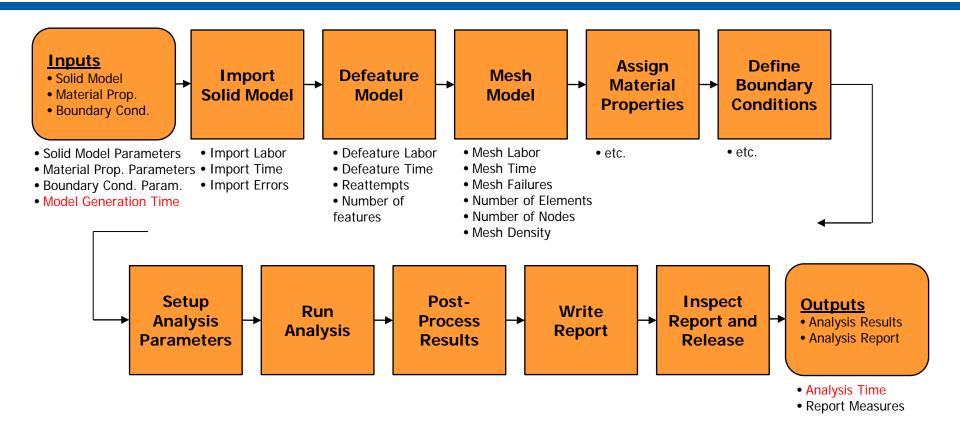

# Analysis Time Process Example

- · For each subprocess identify measures that may contribute to the characteristic of interest

- · Model may be dependent upon how one process or subprocess affects another

# How will one process affect another?

| \ Effect<br>Cause \         | Requirements<br>Development                                                                   | Technical<br>Solutions                                                                                                                    | Product<br>Integration                                                                                    | Verification                                                                                                                             |

|-----------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Requirements<br>Development | • How does the<br>quantity of<br>requirements affect<br>the requirements<br>development time? | <ul> <li>How will reqmts.<br/>affect analysis time?</li> <li>How does<br/>requirements<br/>maturity impact HW<br/>design time?</li> </ul> | How will<br>requirements affect<br>assembly time?                                                         | • How does the<br>quantity of<br>requirements affect<br>test cost and<br>schedule?                                                       |

| Technical<br>Solutions      |                                                                                               | • How does the<br>drawing generation<br>time and quantity of<br>errors found affect<br>procurement time?                                  | • How does the<br>drawing generation<br>time and quantity of<br>errors found affect<br>integration time?  | <ul> <li>How does analysis<br/>time affect testing<br/>success?</li> <li>How does<br/>prototyping affect<br/>testing success?</li> </ul> |

| Product<br>Integrations     |                                                                                               |                                                                                                                                           | • How does standard<br>part usage, design<br>reuse, and other part<br>selections affect<br>assembly time? | How does<br>integration time<br>impact system testing<br>time and number of<br>failures?                                                 |

| Verification                |                                                                                               |                                                                                                                                           | • How does<br>component testing<br>affect integration<br>time?                                            | How do design<br>review scores impact<br>testing time?                                                                                   |

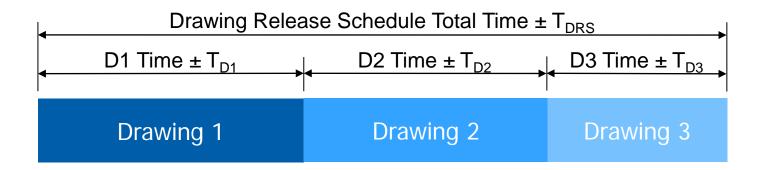

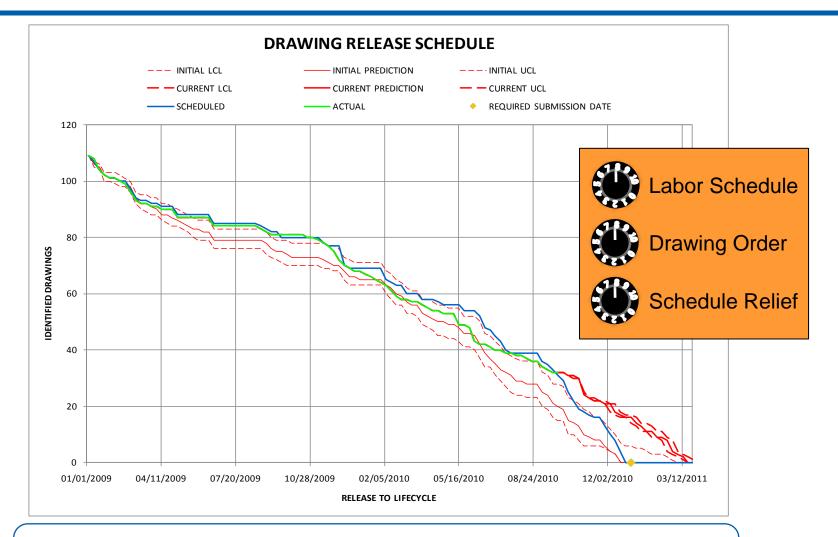

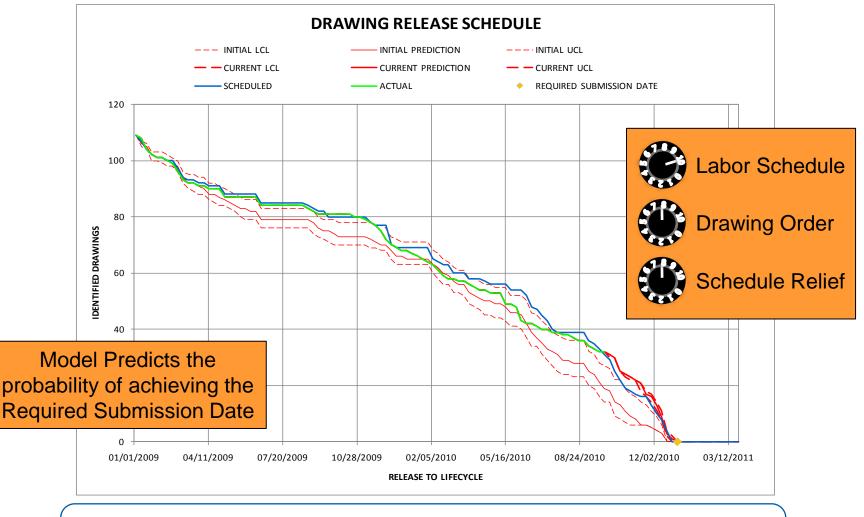

# Drawing Release Schedule (DRS) PPM

- Engineering drawings are a major work product for hardware engineering

- Once the design has been reviewed and deemed ready for procurement drawings are generated, inspected, and released to CM, in series

- Hardware procurement is dependent upon the timely release of drawings

- Engineering, Project Management, and Operations are interested to know when drawings will be released and to manage the Drawing Release Schedule

The DRS PPM forecasts when drawings will be completed and indicates when the schedule is off track

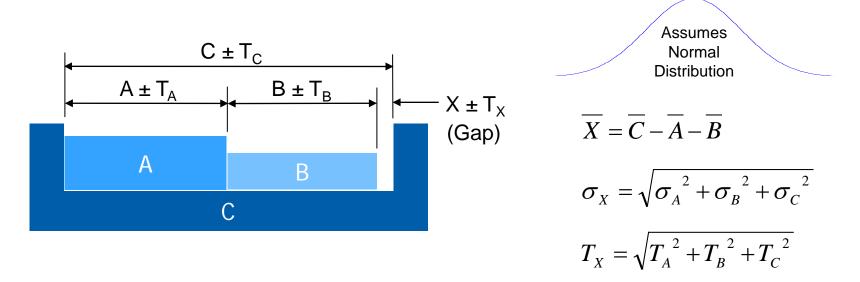

• Lets begin with something familiar to mechanical engineers...

- Statistical Tolerance Stacking allows the designer to evaluate the effect part tolerances will have on critical interfaces of a higher level assembly. (Product attributes are used to predict product attributes.)

- How can a similar approach be used to predict process performance?

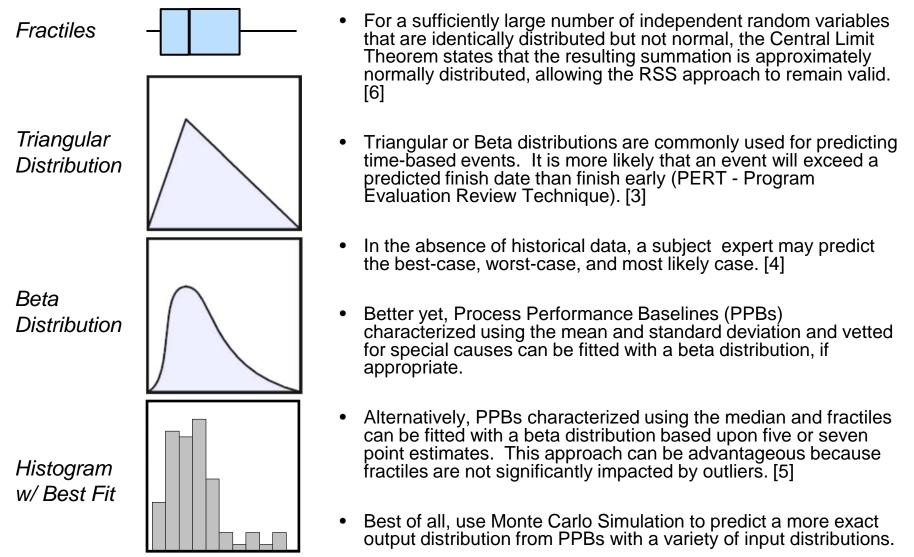

• Method works well for time durations or labor hours summing in series

Drawing 1 + Drawing 2 + Drawing 3 = Drawing Release Schedule

Process A + Process B + Process C = Composed Process

Iteration 1 + Iteration 2 + Iteration 3 = Analysis Time

Test A + Test B + Test C = Total Test Time

CCA Design + PWB Layout + CCA Procurement Time

# Drawing Release Schedule (DRS) PPM

Model predicts DRS based upon statistical stack-up of drawing generation, review, and release cycle times.

# Drawing Release Schedule (DRS) PPM

A violation of statistical limits invokes corrective action, typically an increase in devoted labor hours.

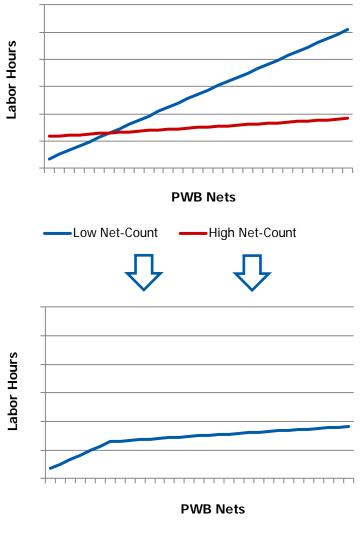

# Printed Wiring Board (PWB) Layout Labor Forecasting PPM

- The Design Layout Technology (DLT) group lays out where components will be placed on a Printed Wiring Board (PWB) and the layers, vias, and traces that will connect them

- Historically, the workload in this area has been difficult to manage (very up and down)

- DLT was interested in being able to predict their upcoming workload accurately based upon board complexities in order to adjust controllable factors and meet these demands.

The PWB Layout PPM forecasts the workload for the DLT group and allows for the management of labor

# Generating a Linear Regression Model

- Complexity Factors

- Component Count

- Number of Nets

- Number of Pins

- Number of Vias

- Number of Connections

- Number of Vias per Connection

- Number of PWB Layers

- Number of Padstacks

- Strong correlation discovered between Labor Hours and PWB Net count

- Two-stage linear regression model established

0.75

1.50

9.7

0.76

1.18

1.50

1.00

1.25

9.52

1.33

1.27

1.25

3.85

| PWB Desi                     | -                           |                                                 |                                                                   |                                                            |                                                                   |                                             |                                      |     |                       |                                |                                   |                                   |        |        |        |         |         |      |

|------------------------------|-----------------------------|-------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------|--------------------------------------|-----|-----------------------|--------------------------------|-----------------------------------|-----------------------------------|--------|--------|--------|---------|---------|------|

| Prediction/Estimator Tool 95 |                             | 95% Predic                                      | 95% Prediction Interval Ac                                        |                                                            | Actuals                                                           |                                             |                                      | Pro | posec                 | Hand                           | ling of PWB Design                | Manpower Scheduling               |        |        |        |         |         |      |

| CCA Board<br>Number          | Number<br>of Nets<br>w/Rats | Month<br>Scheduled<br>To Start<br>PWB<br>Design | Lower<br>PWB<br>Design<br>Labor<br>Prediction<br>Limit<br>(Hours) | Average<br>PWB<br>Design<br>Labor<br>Prediction<br>(Hours) | Upper<br>PWB<br>Design<br>Labor<br>Prediction<br>Limit<br>(Hours) | Actual<br>PWB<br>Design<br>Labor<br>(Hours) | Average<br>Predicte<br>Man<br>Months |     | Authorize<br>Overtime | Temporarily Hire<br>Contractor | Reschedule Start<br>Of PWB Design | Comments                          | Sen-09 | Oct-09 | Nov-09 | De c-09 | .lan-10 | Feb- |

|                              | Withde                      | Doolgii                                         | (1.0010)                                                          |                                                            | (110410)                                                          | (nouro)                                     | monthe                               |     |                       | 1                              | /                                 | DLT and PMO concur on labor       |        | 001 00 | 101 00 | 200 00  | our ro  |      |

|                              |                             |                                                 |                                                                   |                                                            |                                                                   |                                             |                                      |     |                       |                                |                                   | resolution, board not in critical |        |        |        |         |         | l    |

|                              |                             |                                                 |                                                                   |                                                            |                                                                   |                                             |                                      |     |                       |                                |                                   | path, no special handling         |        |        |        |         |         | 1    |

|                              |                             |                                                 | Overtime                                                          |                                                            |                                                                   |                                             |                                      | Yes | No                    | No                             | No                                | required                          | 1.29   |        |        |         |         | ł    |

|                              |                             |                                                 |                                                                   |                                                            |                                                                   |                                             |                                      |     |                       | 17                             |                                   | DLT and PMO concur on labor       |        |        |        |         |         | í —  |

|                              |                             |                                                 |                                                                   |                                                            |                                                                   |                                             |                                      |     |                       |                                |                                   | resolution, board not in critical |        |        |        |         |         | ł    |

|                              |                             |                                                 |                                                                   |                                                            |                                                                   |                                             |                                      |     |                       | V                              |                                   | path, no special handling         |        |        |        |         |         | 1    |

|                              |                             |                                                 |                                                                   |                                                            |                                                                   |                                             | Yes                                  | No/ | No                    | No                             | required                          | 1.60                              |        |        |        |         | I       |      |

|                              |                             |                                                 |                                                                   | 🖌 Ter                                                      | npora                                                             | rv Hi                                       | re                                   |     |                       |                                |                                   | DLT and PMOconcur on labor        |        |        |        |         |         | 1    |

|                              |                             |                                                 |                                                                   |                                                            | npora                                                             |                                             |                                      |     | V                     |                                |                                   | resolution, board is in critical  |        |        |        |         |         | 1    |

|                              |                             |                                                 |                                                                   |                                                            |                                                                   |                                             |                                      |     | Ϊ.,                   |                                |                                   | path, special handling required   |        |        | 0.45   |         |         | l    |

|                              |                             |                                                 |                                                                   |                                                            |                                                                   |                                             |                                      | No/ | Yes                   | No                             | No                                | DLT and PMO concur on labor       |        | 4      | 3.45   |         |         |      |

|                              |                             |                                                 |                                                                   | BPO                                                        | sched                                                             |                                             |                                      |     |                       |                                |                                   | resolution, board is in critical  |        |        |        |         |         | 1    |

|                              |                             |                                                 |                                                                   |                                                            | SCHEU                                                             | iule                                        |                                      | X   |                       |                                |                                   | path, special handling required   |        |        |        |         |         | ł    |

|                              |                             |                                                 |                                                                   | <b>7</b>                                                   |                                                                   |                                             |                                      | No  | Yes                   | Yes                            | No                                | path, special handling required   |        |        | 4.00   | 3.83    |         | l    |

|                              |                             |                                                 |                                                                   |                                                            |                                                                   |                                             |                                      |     | res                   | res                            | INU                               | DLT and PMO concur on labor       |        |        | 4.00   | 3.83    |         |      |

|                              |                             |                                                 |                                                                   |                                                            |                                                                   |                                             |                                      |     |                       |                                |                                   | resolution, board not in critical |        |        |        |         |         | l    |

Yes

No

No

No

No

No

Yes

Yes

Yes

Yes

No

No

No

Yes No

No

No

No

No

No

path, no special handling

required

Prior direction provided to DLT

for handling

Prior direction provided to DLT

for handling

Prior direction provided to DLT for handling

DLT and PMO concur on labor

resolution

Total Number Of Man-Months

2.89

#### DLT Labor Prediction PPM provides:

- Ability for Project and DLT organization to control scheduling and costs for design of PWBs

- Ability to predict DLT labor requirements, as well as prediction interval

- Model allows for feedback of actual labor requirements for monitoring and control

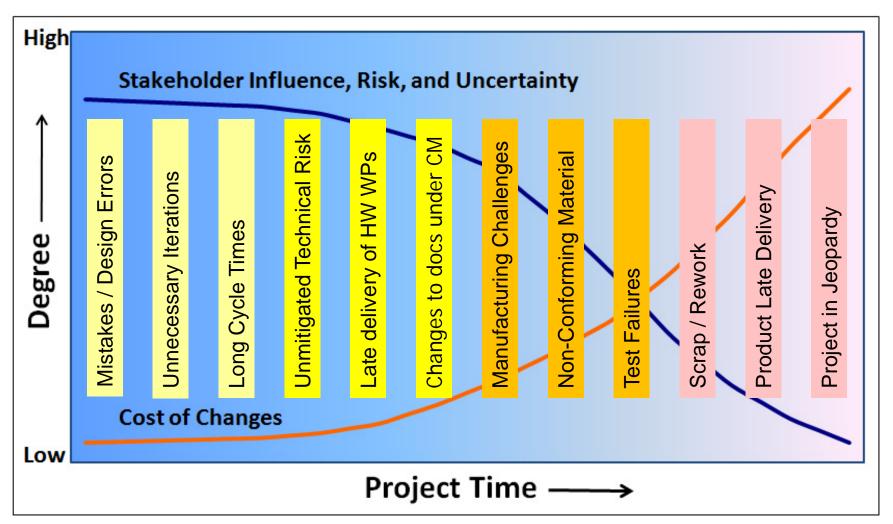

### What do Hardware Engineers Care to Avoid?

NORTHROP GRUMMAN

• Often we think about manufacturing and assembly as production processes, but they are development processes as well

- "Use effective methods to implement the product components" [1] (TS SP3.1, Subpractice 1)

- "Assemble product components" [1] (PI SP3.2)

- Best practice advises that a component be designed with the manufacturing and assembly processes in mind

- It is the responsibility of the hardware engineer to consider manufacturing and assembly costs throughout the development process (the earlier the better!)

- Take advantage of process baselines from manufacturing focused process improvement initiatives, such as Six Sigma, Lean, and Total Quality Management, to devise Process Performance Models that offer insight into the development process.

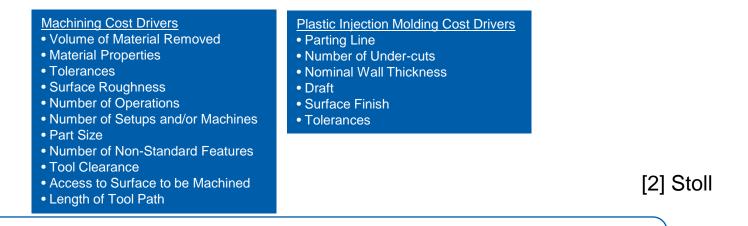

# Considerations for a DFM PPM

• How do the manufacturing processes selected during the design phase affect the manufacturing cost?

• How do product and process parameters affect manufacturing process cost?

NORTHROP GRUMMAN

A PPM predicting manufacturing process cost would depend upon process selections and product and process parameters

#### Considerations for a DFA PPM

How do product and process parameters affect assembly process cost?

Assembly Cost =

$$\sum_{i=1}^{m} (C_H + C_I + C_S + C_A + C_V)_i + \sum_{j=1}^{n} (C_{SO} + C_V)_j$$

m = total number of parts or subassemblies

n =total number of separate operations

$C_H$  = handling cost

$C_I =$ insertion cost

- $C_s$  = securing cost

- $C_A$  = adjustment cost

- $C_V$  = verification cost

- $C_{SO}$  = separate operation cost

Assembly Cost Drivers

- Number of Parts

- Number of Fasteners

- Part Commonality

- Standard Part Usage

- Assembly Sequence

- Part Handling

- Part Insertion

- Part Securing

- Adjustments

- Verification

- Number of separate operations

- Tolerances

[2] Stoll

A PPM predicting assembly process cost would depend upon product and process cost driving parameters

- [1] Chrissis, Mary Beth, Mike Konrad, and Sandy Shrum. *CMMI Second Edition Guidelines for Process Integration and Product Improvement,* Addison-Wesley, Boston, 2007.

- [2] Stoll, Henry W. Product Design Methods and Practices. Marcel Dekker, Inc., New York, 1999.

- [3] Gray, Clifford F., and Erik W. Larson. *Project Management The Managerial Process*, McGraw-Hill Irwin, Boston, 2008.

- [4] Software Engineering Institute, *Understanding CMMI High Maturity Practices*, Carnegie Mellon University, 2007.

- [5] Zhang, Yue. A simple and logical alternative for making PERT time estimates, IIE Transactions, 1996.

- [6] Siegel, Andrew F. Practical Business Statistics. McGraw-Hill Irwin, Boston, 2000.

- [7] <u>http://en.wikipedia.org/wiki/Central\_limit\_theorem</u>, Oct. 11, 2010.

# **Questions?**

- Looking for something a little more...hard-hitting? Well, this presentation is not for softies and it is guaranteed to hit close to home with hardware engineers. Learn tactics and techniques that hardware engineers can put directly to use.

- We will begin with a look at common hardware development processes and identify some aspects that lend themselves to modeling.

- Next, we will identify what we want to predict and what measures and baselines are needed to establish a model.

- We will look at some modeling techniques and some examples of hardware PPMs used at the Northrop Grumman Electronic Systems Rolling Meadows Campus, a CMMI Level 5 organization.

- Finally we will talk about the value and potential benefits of these models. Join us for a rock-solid approach to hardware process performance models.